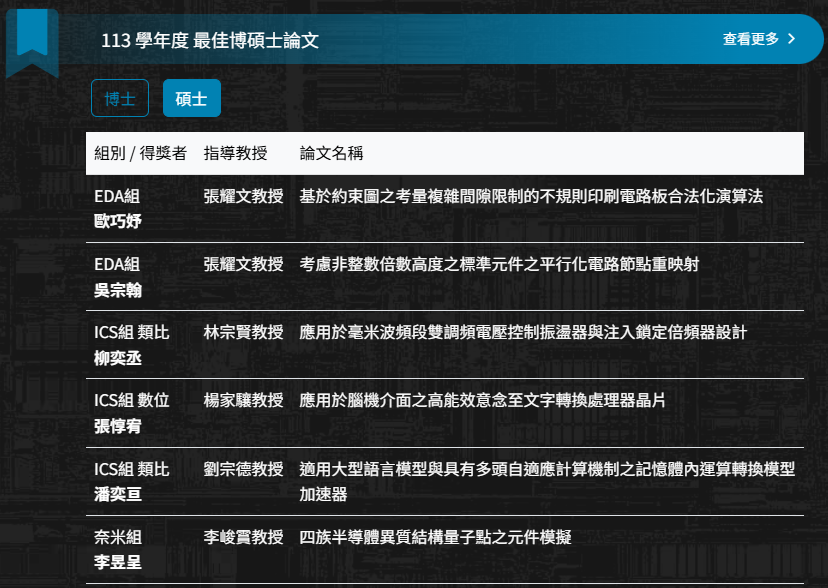

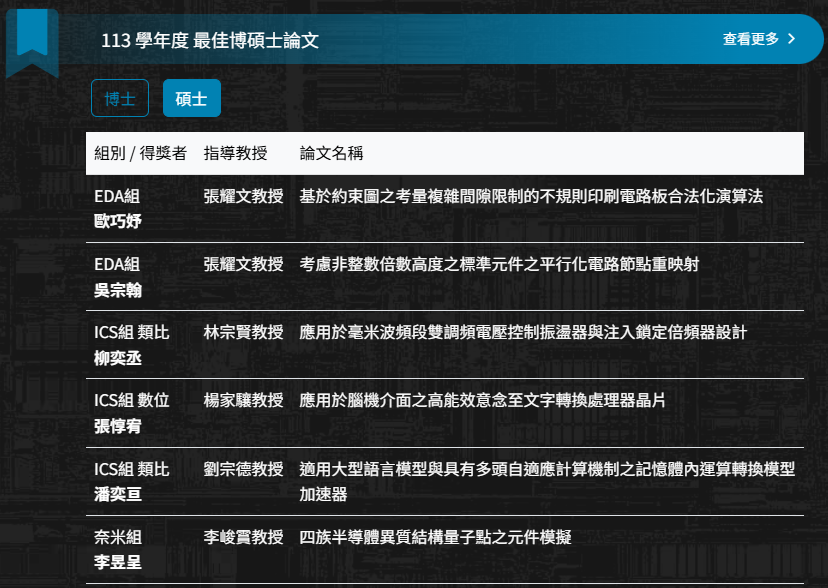

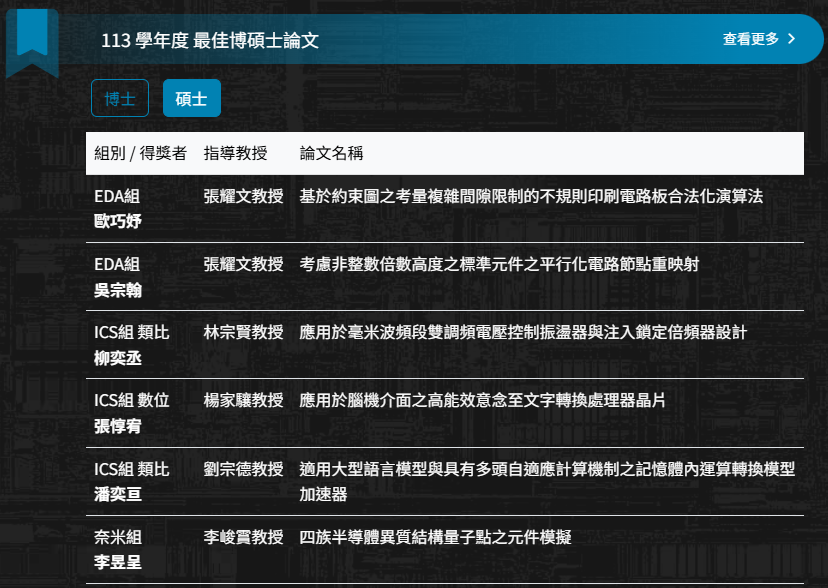

[獲獎]恭喜 柳奕丞 學長 榮獲 113 學年度 最佳碩博士論文

Y.-H. Wang, Y.-G. Yeh, and T.-H. Lin, “An 84.8-dB SNDR 62.5-kHz Bandwidth 2nd-order Noise-Shaping SAR ADC with a Duty-Cycled OTA Sharing Technique,” IEEE VLSI-TSA, Apr. 2025.

C.-H. Fang et al., “A 185-μW, ±2.5-ppm -40°C-80°C Analog TCXO With A Differential-Pair-Based Polynomial Temperature Compensation Technique,” IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 1-3, Nov. 2024.